# HT4179 Transmission IC for RFID read only

# **Summary**

HT4179 is the RFID read transmission circuit that is formed by CMOS. The electronic power is provided by the electronic coil of HT4179's 2 pins, and the operation pulse is provided through the same path. HT4179's application is to adjust radio frequency to make 64 bits data loading on RF. This is the reason that HT4179 can transfer data by RFID.

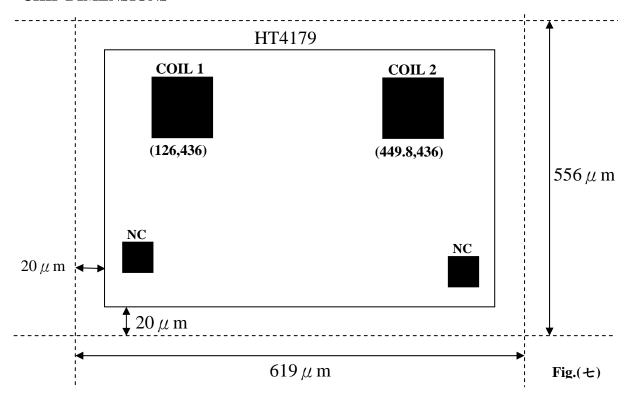

## **Outside circuit**

Fig.(—)

IC capacitor 540pF

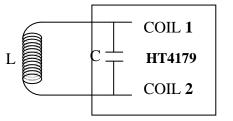

# HT4179's pin Assignment

## HT4179

COIL1 / CLOCK INPUT

COIL2 / DATA TRANSMISSION

PAD size 90um\*90um

Chip size 579umx516um

Fig.(=)

#### **Electronic condition**

Table (—)

| Parameter                               | Min        | Typical | Max  | Unit                                                 |

|-----------------------------------------|------------|---------|------|------------------------------------------------------|

| operation temperature operation voltage | -40<br>3.5 | 5       | +85  | $^{\circ}_{\mathbf{V}}$                              |

| operation frequency                     | 100        | J       | 150  | MHz                                                  |

| storage temperature<br>ESD capability   | -55        | 2000    | +200 | $egin{array}{c} \mathbb{C} \ \mathbf{V} \end{array}$ |

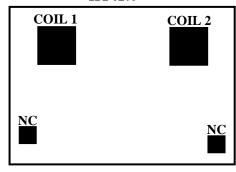

# **Code Format**

Fig.(三)

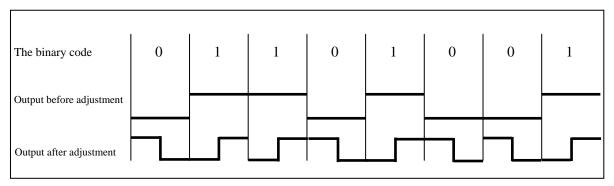

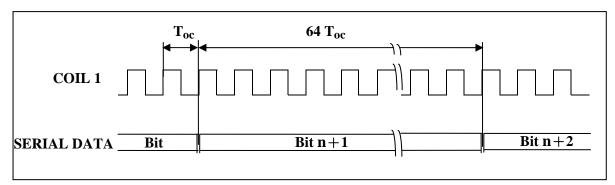

# **TIMING**

Fig.(四)

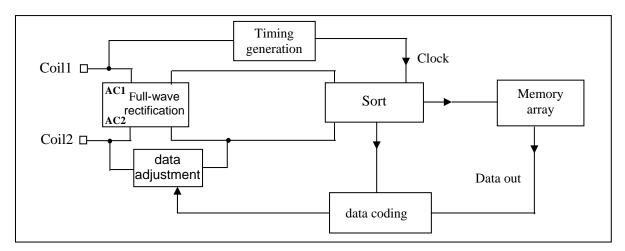

# **IC BLOCK**

Fig.(五)

#### **MEMORY ARRAY**

THE HT4179 CONTAINS 64 BITS DIVIDED IN FIVE GROUPS OF INFORMATION. 9 BITS ARE USED FOR THE HEADER, 10 ROW PARITY BITS (P0-P9), 4 COLUMN PARITY BITS (PC0-PC3), 40 DATA BITS (D00-D93), AND 1 STOP BIT SET TO LOGIC 0.

| 1 1 1 1            | 1            | 1           | 1          | 1          | 1         | - 9 BITS HEADER              |

|--------------------|--------------|-------------|------------|------------|-----------|------------------------------|

| 8 VERSION BITS OR  | <b>D00</b>   | <b>D01</b>  | <b>D02</b> | D03        | <b>P0</b> | - 4 DATA BITS AND            |

| CUSTOMER ID        | <b>D10</b> 1 | D11         | <b>D12</b> | D13        | <b>P1</b> | ASSOCIATED EVEN ROW PARIY    |

|                    | <b>D20</b>   | <b>D21</b>  | <b>D22</b> | D23        | <b>P2</b> | BIT                          |

|                    | <b>D30</b> 1 | D31         | <b>D32</b> | D33        | <b>P3</b> |                              |

| 32 DATA BITS       | <b>D40</b> 1 | <b>D41</b>  | <b>D42</b> | <b>D43</b> | <b>P4</b> |                              |

| ALLOWING 4 BILLION | <b>D50</b> 1 | D51         | <b>D52</b> | <b>D53</b> | P5        |                              |

| OF COMBINATIONS    | <b>D60</b> 1 | <b>D61</b>  | <b>D62</b> | D63        | <b>P6</b> |                              |

|                    | <b>D70</b> 1 | <b>D7</b> 1 | <b>D72</b> | D73        | <b>P7</b> |                              |

|                    | <b>D80</b> 1 | <b>D81</b>  | <b>D82</b> | <b>D83</b> | <b>P8</b> | - 4 COLUMN EVEN PARITY BITS, |

|                    | <b>D90</b> 1 | D91         | <b>D92</b> | D93        | P9        | NO ROW PARITY BIT            |

|                    | PC0          | PC1         | PC2        | PC3        | 0         |                              |

Fig.(六)

THE HEADER IS COMPOSED BY THE 9 FIRST BITS WHICH ARE MASK PROGRAMMED TO 1 1 1 1 1 1 1 1 1 1 1 DUE TO THE DATA AND PARITY ORGANISATION, THIS SEQUENCE CANNOT BE REPRODUCED IN THE DATA STRING. THE HEADER IS FOLLOWED BY 10 GROUPS OF 4 DATA BITS AND 1 EVEN ROW PARITY BIT. THEN, THE LAST GROUP CONSISTS OF 4 EVEN COLUMN PARITY BITS WITHOUT ROW PARITY BIT. BITS D00 TO D03 AND BITS D10 TO D13 ARE CUSTOMER SPECIFIC IDENTIFICATION.

THESE 64 BITS ARE OUTPUTTED SERIALLY IN ORDER TO CONTROL THE MODULATOR USED TO MODIFY THE CURRENT AT ONE OF THE COIL TERMINALS. WHEN THE 64 BITS DATA STRING IS OUTPUTTED, THE OUTPUT SEQUENCE IS REPEATED CONTINUOUSLY UNTIL POWER GOES OFF.

### **CHIP DIMENSIONS**